ReSpecT-2 (128k)

Last Update - 18 March 2007

ReSpecT2PCB.gif & ReSpecT2SCH.gif - схема и платка . Размер платки примерно 15,97 x 8,21 см .

http://zx.pk.ru/showthread.php?t=3957&goto=lastpost

Начальные и конечные значения сигналов выставленны приблезительно .

ReSpect2 V2.0 AHDL by Z.A.N. © SBLive.narod.ru Данный вариант сделан отчасти по мативам SpeccyBob/RealSpeccy . По сравнению со схемой SpeccyBob , в этом варианте убран отдельный счётчик "экрана". Также убрано шаманское торможение экрана в разных областях оного и на бордюре процессор не тормозится . Видео контроллер всё так же отжирает по одному такту на байт при работе процессора в экранной области (пол такта на загрузку атрибута и пол такта на загрузку пикселей). Экран сдвинут на один такт процессора (было полтора). Добавленно отдельное гашение и фиксированный INT (с.м. рисунок формирования экрана). Шина адреса процессора берется с шины видео адреса ВК VA[13..0] и отдельно заведённых адресных битов A15, A14 . На время работы видео контроллера (пол такта CPU x2) адреса ранее считанные с ША процессора через VA[13..0] и A15, A14 сохраняются(удерживаются) на буфере VA_BUF_IN[15..0] (на пол такта CPU). Для устройств которым достаточно для дешифрации A15, A14 могут их брать не с VA_BUF_IN[15..0] а прямо с A15, A14 . Сделан режим 4BIT Per Pixel и возможность выбора разрешения для данного режима 256x192 , 256x224 , 256x256 , 320x200 . Впринципе эти же разрешения можно применить и для режима 1BIT Per Pixel если передвинуть область атрибутов . Также можно убрать перемешивание строк .

Торможение

при обращении к порту FE так же убрано .

При чтение из порта

FF , будет считываться состояние шины VD , т.е. именно то что считывается

на оригинальном спектруме .

В будущем варианте с турбо-режимом до 21MHz планируется завезти ШД CPU целиком в матрицу (без перспективы отгрызания лишних бит) чтение/запись из/в VRAM будет происходить через матрицу . Вместо резюков между ША CPU и ША VRAM будут поставленны регистры (дабы уменьшить время наростания сигналов). Резюки между ШД CPU и ШД VRAM останутся для выполнения функции порта FF , хотя вероятно их следует убрать .

Вариант платки под четыре чипа SRAM по 32килобайт. Свободных пинов остаётся всёго три (если не делать раздельные H/V Sync) . Шина данных полностью заведена в матрицу , перекачка в/из VRAM только через неё . Резюки междуду ШД CPU и ШД VRAM выполняют функцию порта FF .

Видео режим 4BIT Per Pixel (16 цветов на точку) by AlCo .

Каждый пиксель отображается четырьмя битами разом . Для отображения пикселей используется только регистры атрибутов и выхлопной мультиплексор , сдвиговый регистр байта пикселей не используется , счётчик должен быть залочен на генерацию адресов пикселей . Пока в первый регистр закачиваются данные из второго читает мультиплексор . В байте хранятся два пикселя по четыре бита . Для их отображения необходимо изменить способ поступения битов с регистра на мультиплексор , т.к. в качестве первого (левого) пиксиля байта используется комбинация битов INK RGB+BRIGHT , а в качестве второго (правого) пикселя байта используется комбинация битов PAPER RGB+FLASH . На выхлопной мультиплексор нужно вместо бита PAPER BRIGHT подать с атрибутного регистра бит FLASH . Переключение между левым и правым пикселем осуществляется частотой 3,5MHz , которая подаётся вместо сигнала переключавшего INK/PAPER . Низкий уровень - левый пиксель , высокий уровень правый пиксель . Регистры атрибутов заряжаются на частоте 3,5MHz по положительному перепаду (с.м. рисунок) . Экран использует две видео страницы (RAM5 и RAM7) которые как бы поделены на две половинки каждая . Последовательность чтения байтов в регистры - RAM7 первая половинка (hC000) , RAM5 первая половинка (h4000) , RAM7 вторая половинка (hE000) , RAM5 вторая половинка (H6000). Для реализации этого необходимо подать на VA13 частоту 0,875MHz , отвечающую за выбор половинок в страницах . Низкий уровень - первая половинка , высокий уровень - вторая половинка . Так же на пин выбора RAM7 / RAM5 необходимо подать частоту 1,75MHz . Низкий уровень - RAM5 , высокий уровень - RAM7 .

При работе процессора в VRAM (RAM7&RAM5) впринципе можно минимизоровать простой процессора до четверти такта (и меньше) каждого такта 3,5MHz , т.к. первый регистр атрибутов загружается по положительному перепаду частоты 3,5MHz . Процессор не тормозится вовсе если работает не в VRAM .

Коментарии к описанию и рисунку - На пентагоне INK выбирается низким уровнем , PAPER высоким . В ReSpecT - Первый пиксель (INK) выбирается высоким уровнем , второй (PAPER) выбирается низким уровнем .

Времянки

загрузи первого атрибутного регистра и распределение VACC и CACC ещё окончательно

не определены .

Регистр палитры aka накрутчик палитры .

http://zx.pk.ru/showthread.php?t=4767&goto=lastpost

Так называемый накрутчик палитры (регистр палитры) , идеально подходит для режима 16 цветов на точку , т.к. даёт гораздо больший эффект нежели при использовании со знокоместовым режимом . Принцип действия достаточно прост , на полученную комбинацию бит с цифровых контактов RGBY , устройство подставляет уникальный оттенок из предварительно загруженной в него палитры . Реализация устройства может быть любой , от рассыпухи до однокристалок (последний вариант более предпочтителен).

В качестве примера подобного устройства , ниже дано описание старого варианта устройства от В.М.Г. . Повторять именно такой вариант смысла не вижу , т.к. используются аж три порта , и на цветовой канал приходятся всего четыре бита (к тому же инверсных), а можно без особого труда сделать восемь бит на канал (но реализация на МК будет несколько затруднена , т.к. совсем не остаётся пинов для управления). Сомо устройство по принципу управления будет похоже на любое программно управляемое устройство (например как муз.сопр.), с аналогичным принципом выбора регистров и записи вних информации . Подключить это устройство можно так же как подключен второй муз. сопр. в турбо-саунд , вследствии чего не нужно будет использовать отдельные порты для управления устройством .

Схемы

от В.М.Г. Выпуск 11.

Расширенная графика. Регистр палитры.

Это перенабивка со сканограммы которую предоставил Spensor (10X!!!).

Сравнительно крупные точки во втором режиме расширенной графики на "Спектруме" вызывают эффект алейзинга - неприятного излома линий . Этот эффект можно в значительной мере уменьшить , если цвета будут плавно переходить один в другой . Данная схема позволяет использовать на экране "ZX-Spectrum'а" 4096 цветов (одновременно любые 16 из одного набора), благодаря чему появляется возможность для более натурального раскрашивания картинок и создания новых видеоэффектов . Подключение режима аппаратное (пока), установка палитры - программая .

Доработка подключается к компьютеру 22-мя проводами (вместе с питанием) и изменений на плате не требуется .

Сигнал DB , DR , DG , DY (цифровые цвета) берутся из компьютера с выходов мультиплексора КП11 (КП12 , КП2) либо с других микросхем до резисторов . Сигнал -BLANK (гашение) берётся с той же КП11 (КП12 , КП2) со входа OE и инвертируется ; в крайнем случае можно использовать SYNC или даже -BORDER . 7MHz берётся с 9 вывода (тактовая частота) ИР16 , сигнал DOS , высокий уровень обозначает включение контроллера дисковода . Некоторые контроллеры вырабатывают только инверсный сигнал -DOS , тогда этот сигнал подключается к 6-му выводу D2 , а к 5-му M1 (сппроцессора через инвертор). Остальные сигналы берутся с прощессора Z80 . Первые два символа в обозначении выходов 155 РУ2 указывают на микросхему , с которой эти сигналы берутся . Rnew , Gnew , Bnew через 9-контактныйпереключатель подан на R , G , B телевизор ; если их мощности недостаточно , то можно пропорционально уменьшить номиналы выходнах резисторов , либо использовать 3 транзистора КТ315 в качестве эмиттерных повторителей .

ПРОГРАММИРОВАНИЕ . 4096 цветов полуаючаются наложением 3-х основных - красного , зелёного и синего , взятых с различной интенсивностью . Основные цвета имеют по 16 градаций интенсивности , которые устанавливаются младшими битами соответствующих портов :

интенсивность

красного - порт # E7 , биты 0 . . . 3

интенсивность зелёного - порт # EF , биты 0 . . . 3

интенсивность синего - порт # F7 , биты 0 . . . 3

Биты 4 . . . 7 каждого порта определяют : какому старому цвету будет соответствовать данная интенсивность основного : Бит 4 - синему (1 - есть , 0 - нет), бит 5 - красному , бит 6 - зелёному , бит 7 - повышенной яркости . Плюс их сочетания .

Следует учесть , что микросхема 155 РУ2 имеет инверсные выходы . Поэтому максимальной интенсивности цвета соответствует сочетание 0000 младших бит порта палитры .

Для тестироввания устройств выведите на экране изображение из 16-ти широких полос всех возможных для "Спектрума" цветов . Запишите в оба полубайта регистров палитры одинаковые возрастающие последовательности от 0000 до 1111 и включите доработку . На экране цветного телевизора должны присутствовать 16 градаций серого цвета от ярко-белого до чёрного . Если некоторые полооски заметно окашены в отличные от других цвета , то необходимо точнее подобрать номиналы выходных резисторов .

Адреса портов палитры относятся к неиспользуемому у нас устройству InterFace 1 . Длительная проверка показала , что подавляющее большенство программ запись в них не производит . Попытка тестирования компьютером этих портовв момент включения TR DOS блокируется сигналом DOS на микросхеме ИД7 . Таким образом , запрограммировав сразу после включения компьютера регистр палитры , вы можете спокойно пользоваться имеющимися у вас программами .

Далее идёт подсчёт ножек (а не их номера)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 |

CLK IN CLK CPU /MREQ /RD /WR /IORQ /INT /ROM_CE /RAM_CS /VRAM_CS /VRAM_RD /VRAM_WR VD0 VD1 VD2 VD3 VD4 VD5 VD6 VD7 D0 D1 D2 D3 D4 D5 |

- - - |

ReSpecT 48k

Данный вариант клона делается на основе схемы SpeccyBob , которая в свою очередь максимально приблтжена к оригинальному ZX-Spectrum . При использовании данной схемы (с внесением небольших изменений) в качестве основы , освобождается большёе количество контактов матрицы .

На основе данной схемы уже ранее был сделан один клон (автором сайта aticatac.altervista.org), но никаких исходников опубликованно не было . Фотография этого клона представленна ниже .

Клон будет делаться на базе матрицы ALTERA EPM7128SLC84-15 (тот что на фотографии сделан на базе матрицы XILINX) . (Цена матрицы в чип и дэил на текущий момент - EPM7128SLC84-15 410 руб.)

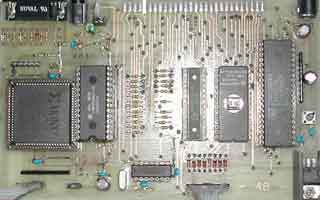

FOTO.jpg - (11 nov 2006) фотка платки для эксперементов .

SBLClock.tif , SBLCPU.tif , SBLVideo.tif - схема SpeccyBob (слегка уменьшенный вариант), схемный ввод проктически полностью идентичен данной схеме .

Ниже идет вольный перевод описания Clock Circuit SpeccyBob :

ОК , я надеюсь что хоть ктонибудь поймёт это ...

Элемент U7C , U7D , U7E совместно с кварцевым резонатором генерируют частоту 14Mhz , которая делится на два , а затем ещё раз на два элементом U13 для получения двух частот - 7Mhz и 3.5Mhz .

Элементы U1 , U2 , U3 (четырёх битные синхронные счётчики) тактуются частотой 7MHz. Элемент U8 совместно с U12 сбрасывают счётчики по достижению ими числа 448 , таким образом формируется счётчик на 448 отсчёта . Это соответствует длинне горизонтальной сканлинии (448 is 224 T-states * 2 because the counter is clocked at 7MHz, not 3.5). (7000:448=15,625)

Низкий уровень сигнала H7 (horizontal video enable) этого счётчика используется как разрешающи отображение картинки по горизонтали (низкий уровень длится 256 отсчётов , затем его сменяет высокий уровень).

Элемнты U9 & U10 генерирують начало и конечец горизонтального синхроимпульса , который окончательно формируется элементом U15B .

Элементы U4, 5 & 6 формируют счётчик вертикальной развёртки . Они тактуются сигналом H7 счётчика горизонтальной развёртки , и подсчитывают скан линии . Элемент U11 совместно с U12C сбрасывают счётчики по достижению ими значения 312 , что соответствыет количеству сканлиний отображаемых на мониторе (в полукадре).

Элемент U14A генерирует вертикальный синхроимпульс . Он очищается одновременно со сбросом вертикального счётчика , и устанавливается снова после конца первой линии (по положительному фронту сигнала R0) .

Элемент U14B генерирует сигнал конца верхней части бордюра . Сбрасывается так же как и вертикальный синхроимпульс вместе со сбросом счётчиков , но устанавливается сигналом R6 (линия 64).

Элемент U15A генерирует сигнал начала нижней части бордюра . Сбрасывается вместе со счётчиками и устанавливается сигналом R8 (линия 256). Зона между 64 и 256 является зоной отображения информации .

Эти два вышеупомянутых сигнала , вместе с H7 (horizontal video enable) поступая на элемент 3ИЛИ-НЕ вырабатывают сигнал Video Enable .

Схема синхрогенератора так же генерирует необходимые синалы для работы видео контроллера . Для этого используется сигнал VE (Video Enable), который управляет передачей пяти сигналав видео контроллеру - S0, S1, S2, Vacc & Cacc.

Эти сигналы преобразуются из сигналов горизонтального счётчика дешифратором U16 (a 3 to 8 line decoder). Сигнал S0 сообщает видео контроллеру что нужно прочесть байт атрибута из памяти . Сигнал S1 ообщает видео контроллеру что нужно прочесть байт пикселей из памяти , и одновременн запустить вывод нового байта . S2 сообщает видео контроллеру что нужно увеличить значение его счётчика на единицу .

Сигналы Vacc и Cacc отвечают за выбор - процесор или видео контроллер имеет доступ к Video RAM. Сигнал Vacc активен при установке в ноль S0 и S1 , Cacc активен при других комбинациях S0 и S1 .

Элементы U16 совместно с U18 так же контролируют доступ к памяти . Если сигнал IOCS (a ULA IO access) или VRAM (A video RAM access) активны , то процесор приостанавливается 'till it is allowed access again.

Элемент U17 задерживает сигнал Video Enable перед передачей на видео контролеер , пока не загрузятся байт атрибутов в первый атрибутный регистр (U2 на схеме ВК) и не загрузится быйт пикселей в сдвиговый регистр (U4 , U5 , U6 на схеме ВК).

|

SpeccyBob Screen

Далее идёт подсчёт ножек (а не их номера)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 |

CLK IN CLK CPU /WAIT |

- - - |

|

Original ZX-Specnrum 48k Screen

Блок схема фирменного ZX-Spectrum .

Процессор приостанавливается при обращении к порту FE , ровно как и при обращении к видео памяти . Это обусловленно тем что не только шина адреса , но и шина данных общие , т.е. шины процессора и видео контроллера объеденены через резисторы . Так же , при обращении к несуществующему порту FF , будет считываться с общей шины данных число считываемое видео контроллером в данный момент времени .